Mã độc phần cứng trong kết cấu FPGA

MỞ ĐẦU

Mảng cổng khả trình (Field-Programmable Gate Array - FPGA) được sử dụng trong nhiều ứng dụng như mạch tích hợp chuyên dụng (Application-Specific Integrated Circuit - ASIC), thiết bị truyền thông, hàng không vũ trụ... và tích hợp sẵn các mô-đun dịch vụ về điện toán đám mây [1], trong đó có thể tạo và thực thi các tùy chọn phần cứng từ trình điều khiển từ xa.

Việc nhập khẩu FPGA và sử dụng lõi sở hữu trí tuệ (Intellectual Property - IP) của bên thứ ba không tin cậy làm tiềm ẩn nhiều nguy cơ chèn HT. Do FPGA chứa một lượng lớn các mạch logic có thể cấu hình lại dưới dạng bảng tra cứu (Lookup table - LUT), khối RAM và các kết nối có thể lập trình được. Điều này đặt ra vấn đề đối phương có thể cấu hình các mạch logic để gây ra những ảnh hưởng nhất định đến hệ thống. HT trong FPGA được chia làm hai loại là phụ thuộc và không phụ thuộc IP [3].

Với HT phụ thuộc IP, đối phương có thể triển khai một Trojan nhằm giám sát các giá trị logic của một số LUT trong FPGA. Khi hoạt động, HT làm sai lệch các giá trị trong LUT và tải vào khối RAM (BRAM), phân phối các giá trị logic trong toàn bộ FPGA.

Đối với HT không phụ thuộc IP, đối phương có thể triển khai một Trojan thành một chip hoàn toàn độc lập với IP. Những Trojan như vậy có thể chiếm một phần nhỏ tài nguyên quan trọng của FPGA và làm sai chức năng, tăng hoặc giảm tần số của xung thiết kế, gây ra sự cố tài nguyên của FPGA, làm tăng độ trễ…

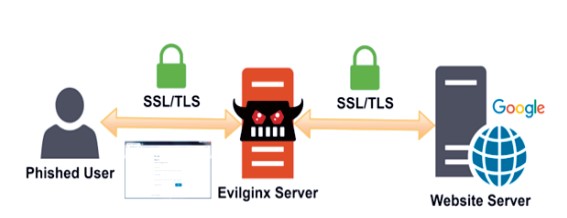

Hình 1. Mô hình rủi ro trong chuỗi cung ứng FPGA [4]

Trong chuỗi cung ứng FPGA, đối phương có thể tham gia ở bất cứ giai đoạn nào như: chèn HT tại xưởng đúc không tin cậy (A1), giảm độ tin cậy của FPGA trong chuỗi cung ứng (A3), chèn HT thông qua công cụ CAD của FPGA. Thậm chí, đối phương có thể đưa các FPGA tái chế vào trong chuỗi cung ứng FPGA (A2).

Hiện nay, ngành công nghiệp chế tạo đang vận hành một chuỗi cung ứng phức tạp, tạo cơ hội cho kẻ ác ý thực hiện ý đồ xấu thông qua việc sản xuất thừa. Cụ thể, xưởng đúc không tin cậy tạo số lượng FPGA nhiều hơn so với yêu cầu hoặc ủy quyền của thiết kế của công ty. Khi đó, đối phương có thể chèn các FPGA lỗi, độc hại vào chuỗi cung ứng mà không cần hiểu biết về thiết kế FPGA. Những FPGA này có thể không được kiểm tra hoặc nếu kiểm tra không đúng cách sẽ nảy sinh các vấn đề về độ tin cậy; hoặc các vấn đề về tái chế, nhân bản, sao chép trái phép…

CÁC CÁCH THỨC CHÈN HT TRONG FPGA

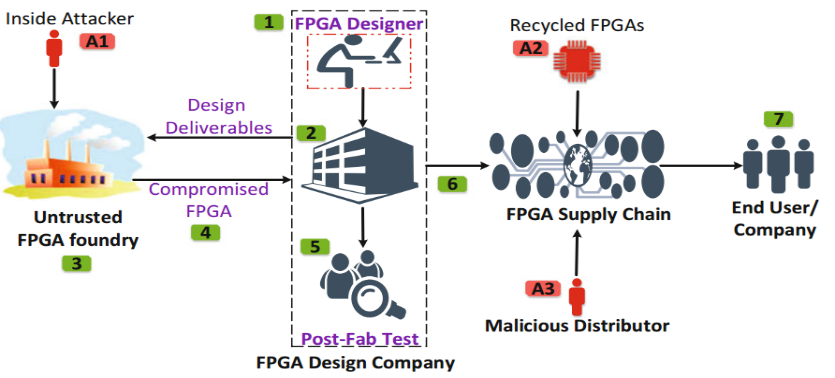

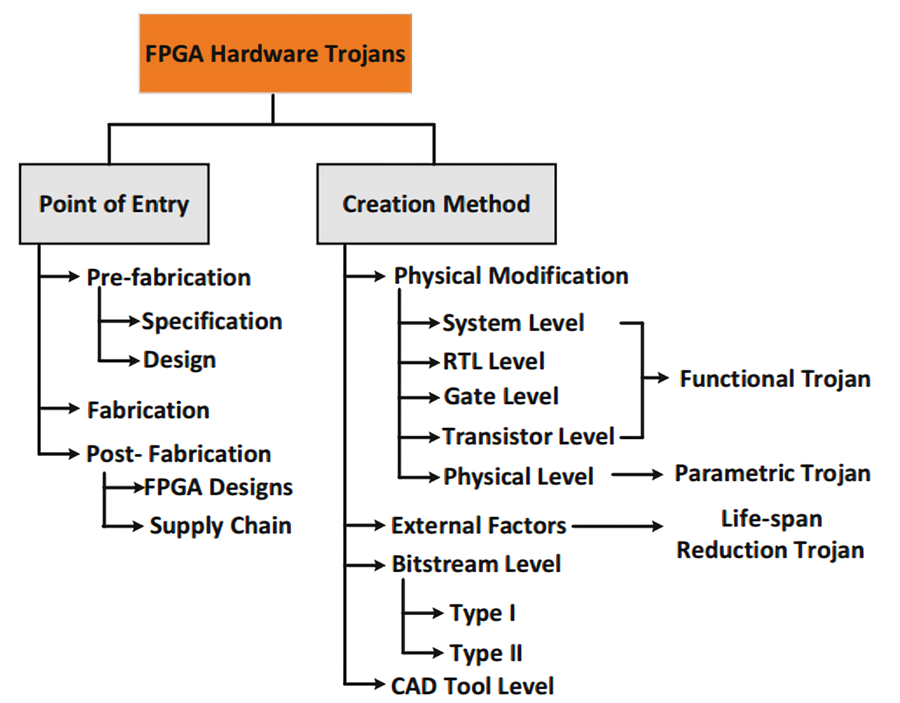

Đối với FPGA, HT có thể bị chèn theo 2 cách là theo điểm chèn vào kết cấu FPGA và theo phương pháp chế tạo.

Cách 1: Theo điểm chèn vào kết cấu FPGA

Theo điểm chèn vào kết cấu FPGA thì các HT có thể được chèn trong giai đoạn trước, trong và sau chế tạo.

Giai đoạn trước khi chế tạo là giai đoạn mà đặc điểm kỹ thuật của các hệ thống như chức năng, kích thước, điện năng tiêu thụ, độ trễ... được hoàn thành. Chèn Trojan trong giai đoạn này sẽ dẫn đến sự thay đổi của thiết kế hoặc các ràng buộc khác như thay đổi thời gian hoặc tăng tần số chuyển mạch. Bên cạnh đó, HT có thể được chèn để kiểm soát chip tại thời điểm khi các FPGA được triển khai.

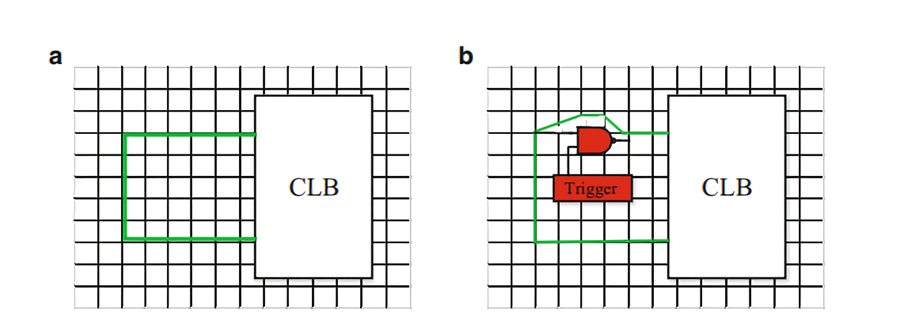

Hình 2. Trojan phần cứng được chèn vào kết cấu FPGA [4]

Trong giai đoạn chế tạo, một tập các mặt nạ thiết kế được tạo ra mạch kỹ thuật số trên một phiến silicon (Wafer Silicon).

Đối với giai đoạn sau chế tạo, Trojan có thể được chèn vào trong những thiết kế RTL/HDL hoặc RTL/HDL cũng có thể được nhập từ các nhà cung cấp IP của bên thứ ba không tin cậy.

Cách 2: Chèn theo phương pháp chế tạo FPGA

Theo phương pháp này thì các HT trong FPGA có thể được phân thành:

- Trojan chức năng (được đưa vào tại một xưởng đúc không tin cậy) thực hiện sửa đổi kết cấu FPGA như thêm, xóa (gate và các transistor), sửa đổi RTL nhưng không làm ảnh hưởng đến chức năng chính của kết cấu FPGA.

- Trojan hoạt hóa tuổi thọ (LRT) là loại Trojan duy nhất không phải được chèn vào phần cứng trong hoặc trước khi chế tạo, mà nó được tạo ra phụ thuộc vào các yếu tố bên ngoài như nhiệt độ cực cao, chùm ion... LRT thúc đẩy quá trình lão hóa hoàn toàn hoặc một phần của kết cấu FPGA, thường được tạo bởi nhà phân phối độc hại trong chuỗi cung ứng FPGA.

Những nhân tố chính thúc đẩy sự lão hóa của FPGA (hoặc bất kỳ IC nào) trong một số yếu tố vật lý là sự mất ổn định nhiệt độ sai lệch âm (Negativebias temperature instability - NBTI) và chèn vào các hạt có hoạt tính cao (Hot carrier injection - HCI). NBTI là thông số điện áp của các transistor như điện áp ngưỡng (Vth) có thể được thay đổi. Chính sự thay đổi này làm giảm hiệu suất các transistor và làm cho các thiết bị lão hóa nhanh hơn.

NBTI chủ yếu ảnh hưởng đến các thiết bị PMOS, còn HCI chủ yếu ảnh hưởng đến NMOS. Trong đó các electron được gia tốc trong kênh có thể va chạm với giao diện cổng oxit, tạo ra các cặp lỗ electron. Vth tăng do các electron tự do bị mắc kẹt trong lớp oxit cổng. Sự suy giảm liên quan đến thuộc tính HCI cho sự cố vật lý và biến dạng đặc trưng của transistor. Sự thay đổi Vth phụ thuộc vào tần số, thời gian và hệ số hoạt động (tỷ lệ chuyển tiếp). Như vậy, cả hai yếu tố dẫn đến sự thay đổi điện áp ngưỡng của các transistor bị ảnh hưởng, với những biểu hiện khi tăng các hoạt động chuyển mạch và độ trễ đường dẫn. Điều này sau đó sẽ ảnh hưởng tới thời gian và làm hao mòn FPGA nhanh hơn.

- Trojan dòng bit lại được chèn bằng cách sửa đổi bitfile của chính nó. Dòng bit có thể được thiết kế ngược để xác định các khu vực của FPGA bị chiếm bởi mạch logic độc hại. Nếu mạch độc hại không ảnh hưởng đến mạch gốc thì gọi là Trojan dòng bit loại I. Ngược lại, nếu sửa đổi mạch ban đầu đối với các khối logic có thể tái cấu hình (Configurable logic block - CLB) hoặc các tài nguyên khác để thực hiện các hoạt động độc hại gọi là Trojan loại II.

- Trojan công cụ CAD là các Trojan nhằm khai thác luồng công cụ CAD để chèn các Trojan ở các định dạng netlist trung gian khác nhau. Những Trojan này có thể được chèn vào một netlist tổng hợp và thậm chí trong ánh xạ hoặc được đặt và định tuyến netlist. Do thiếu tài nguyên để hiểu các định dạng trung gian khác nhau này trong thiết kế, mà những Trojan này có thể dễ dàng tránh được sự phát hiện.

- Trojan làm tăng độ trễ được tạo bằng cách sửa đổi các bảng tra cứu kết nối LUT qua hai CLB. Các Trojan làm tăng độ trễ tương ứng với thay đổi hoặc nhiễu trong bố cục vật lý của FPGA do bổ sung các yếu tố độc hại. Đối phương cần thay đổi silicon FPGA để thêm một Trojan, như khi một Trojan được chèn trong một ma trận CLB hoặc ma trận chuyển đổi định tuyến (Routing switch matrix - RSM), nó sẽ gây nhiễu bố cục vật lý của kết cấu gốc, do đó làm tăng độ trễ. Hình 3a và 3b dưới đây tương ứng là trước khi sửa đổi (CLB FPGA với RSM không có Trojan) và sau khi sửa đổi (Trojan được chèn trong RSM). Điều này cho thấy một Trojan được chèn vào trong một kết nối ảnh hưởng đến độ trễ của lưới, từ đó ảnh hưởng đến tổng độ trễ của đường dẫn kết nối hai chân I/O của CLB. Đường dẫn xem xét được cấu hình là một đường dẫn của bộ tạo dao động vòng RO (Ring oscillator) được lập trình bằng cách sử dụng các LUT tương ứng với các CLB.

Hình 3. Trojan làm xáo trộn kết cấu ban đầu [4]

- Trojan tham số được tạo ra bằng cách sửa đổi các thông số vật lý của thiết bị với mục đích làm giảm độ tin cậy của FPGA.

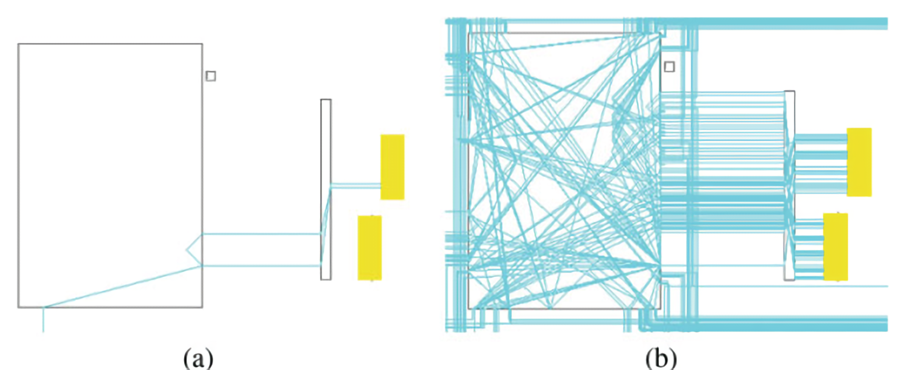

Các Trojan này được triển khai bằng cách thêm các tín hiệu chuyển đổi đồng thời sử dụng các tài nguyên kết nối dày đặc xung quanh một CLB. Điều này tương ứng với việc bổ sung các yếu tố độc hại mà không làm ảnh hưởng đến kết cấu FPGA. Tín hiệu chuyển mạch được kết nối với các dây không được sử dụng và các điểm kết nối lập trình (Programmable interconnect point - PIP). Trojan này làm tăng các hoạt động chuyển mạch, do đó sẽ làm tăng điện năng và tác động đến tần số dao động. Chính sự sụt áp do hoạt động chuyển mạch của Trojan đã ảnh hưởng đến tần số RO.

(a) CLB không có Trojan; (b) CLB có một Trojan

Hình 4. Trojan gây dao động điện áp [4]

KẾT LUẬN

HT có thể gây ra những ảnh hưởng nghiêm trọng đối với kết cấu FPGA, vì vậy việc nghiên cứu các giải pháp phát hiện và ngăn chặn HT là cần thiết. Các kỹ thuật xâm lấn sẽ không khả thi với FPGA, do yêu cầu phần cứng bổ sung, tăng chi phí. Hơn nữa, kỹ thuật đảo ngược thiết kế có thể được sử dụng để kiểm tra một số lượng nhỏ các IC, nhưng không đảm bảo rằng các IC còn lại không bị sửa đổi độc hại. Do đó, cần nghiên cứu một cách kỹ lưỡng các kỹ thuật chống tấn công kênh kề không xâm lấn như vết điện năng tiêu thụ, các giải pháp về độ trễ đường dẫn… kết hợp với quá trình kiểm tra chức năng để đảm bảo an toàn cho FPGA trước mối đe dọa nguy hiểm từ HT.

|

TÀI LIỆU THAM KHẢO 1. Amazon, Amazon EC2 F1 instances – run custom FPGAs in the AWS cloud, https://aws.amazon.com/ec2/instance-types/ f1/. Last accessed 12 May 2017. 2. DARPA, Defense Science Board (DSB) study on high performance microchip supply (2005). 3. S. Mal-Sarkar, A. Krishna, A. Ghosh, S. Bhunia, Hardware Trojan attacks in FPGA devices: threat analysis and effective counter measures, in: Proceedings of the 24th edition of the Great Lakes Symposium on VLSI, ACM, pp. 287–292. 4. Swarup Bhunia, Mark M. Tehranipoor “The Hardware Trojan War: Attacks, Myths and Defenses”, 2018. |

Trần Thị Hạnh, Phạm Minh Đức, Nguyễn Hồng Quân (Học viện Kỹ thuật mật mã)