Mối nguy hiểm từ mã độc phần cứng

Mở đầu

Khi nói đến các thiết bị, người ta thường tập trung vào an toàn phần mềm hoặc an toàn trong quá trình xử lý thông tin, còn phần cứng thì luôn được coi là “tin cậy”. Tuy nhiên, trong những năm gần đây, các vấn đề liên quan đến an toàn phần cứng nhằm đảm bảo sự tin cậy của IC hoặc chip điện tử đã được các nhà khoa học công nghệ tập trung nghiên cứu, trong đó có các chuyên gia của Ban Cơ yếu Chính phủ. Nguyên nhân do hầu hết các IC hiện tại đều được sản xuất chế tạo bởi đối tác thứ ba, phần lớn được nhập khẩu từ các nước khác nhau [1]. Hơn nữa, các IC hiện nay thường chứa các lõi sở hữu trí tuệ (Intellectual Property – IP), modul xây dựng sẵn bởi phía đối tác cho phép tích hợp vào thư viện để hỗ trợ các công cụ tự động hóa thiết kế điện tử (Electronic Design Automation - EDA). Đây chính là một trong những nguyên nhân dẫn đến các thiết bị dễ bị tấn công.

Các HT bắt nguồn từ các Trojan mềm (Software Trojan – ST) nằm trong các bộ công cụ phần mềm phát triển thiết kế phi pháp. Trong suốt quá trình tổng hợp theo luồng thiết kế, HT được chèn cố ý vào mạch điện tổng hợp nhằm gây ra xung đột giữa các thành phần khác nhau của IC. Mỗi thực thể (người dùng, nhà thiết kế, nhà chế tạo, nhà cung cấp) liên quan đến hoạt động thiết kế, chế tạo, kiểm tra, đóng gói và phân phối các IC đều được coi là đối tượng tiềm năng tác động vào IC tại các bước khác nhau trong chu trình thiết kế - chế tạo. Việc cài đặt HT rất đa dạng, vì vậy khó định vị được điểm kích hoạt của loại mã độc này. Khó khăn hơn, HT không thể loại bỏ sau khi IC được chế tạo. Trong khi đó, Trojan mềm có thể dễ dàng bị gỡ bỏ bằng chương trình Anti-Virus [2].

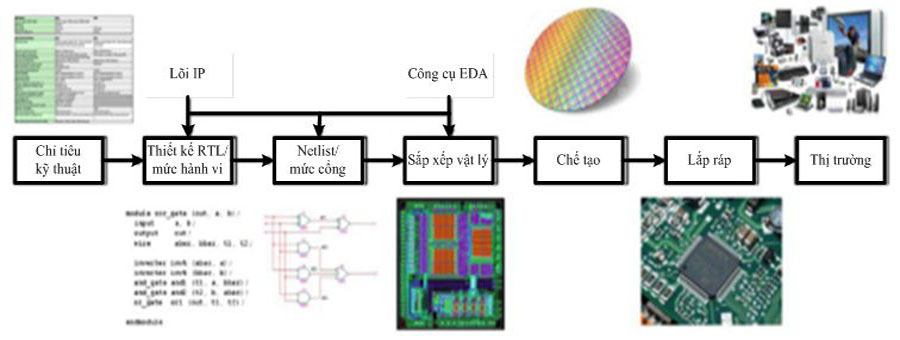

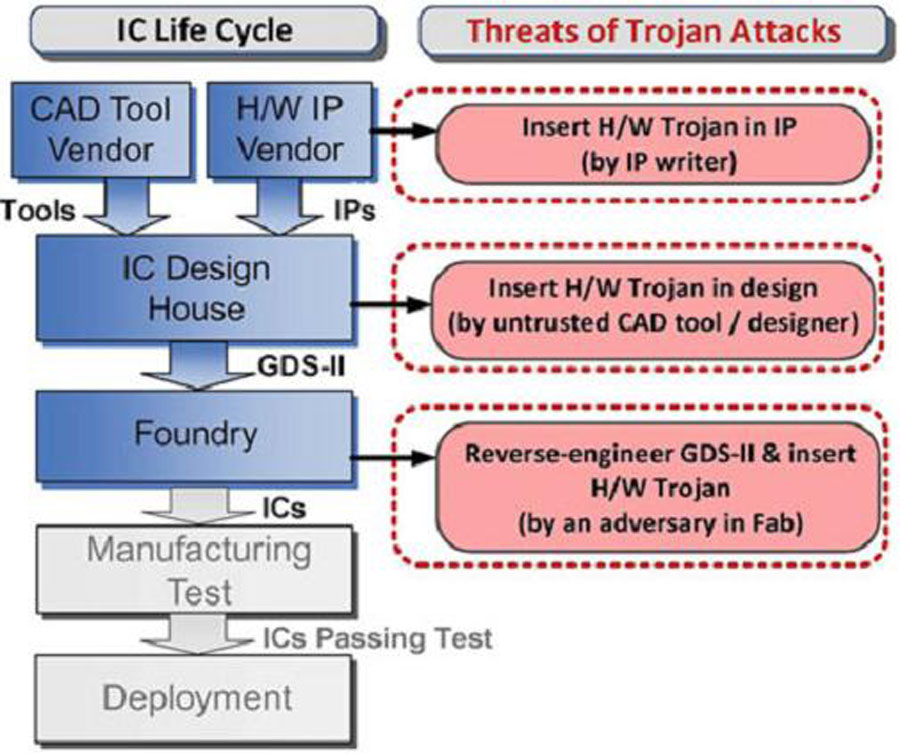

Hình 1: Quy trình thiết kế và chế tạo IC bán dẫn [3]

Đặc điểm chung nhất ở tất cả các đối tượng là cơ hội gây rối thiết kế, có thể chèn HT tại mọi thời điểm làm cho thiết kế nằm ngoài quyền kiểm soát [3]. Trong vòng đời của IC, các cơ hội này diễn tiến ở nhiều giai đoạn khác nhau của chu trình thiết kế - chế tạo (Hình 1, 2 và Bảng 1).

Hình 2: Các giai đoạn dễ tổn thương với HT trong vòng đời của IC [3]

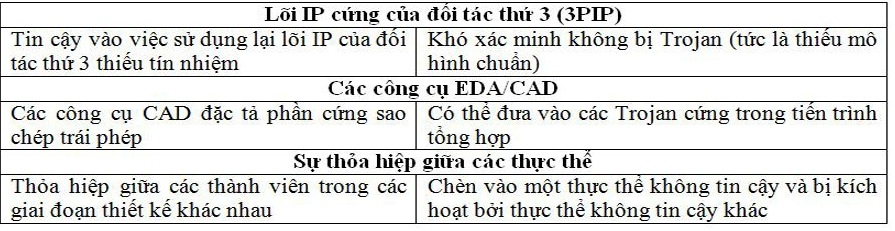

Bàng 1: Các thực thể chèn HT

Cấu tạo HT

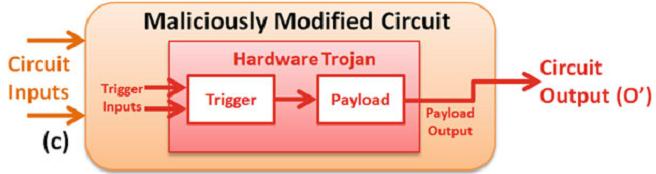

Các Trojan đều được kích hoạt theo một lược đồ xác định (gọi là khối kích hoạt) để thực hiện chức năng chỉ định (tải tin). Bảng 2 tóm tắt sự khác biệt giữa HT và ST.

Bảng 2: So sánh HT và ST

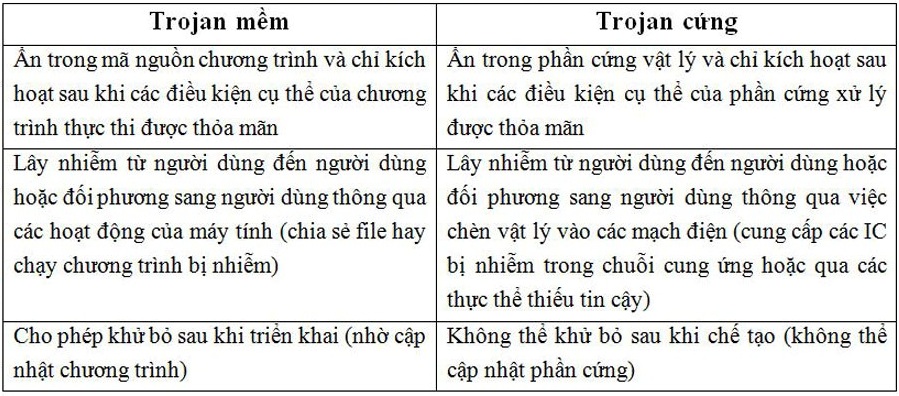

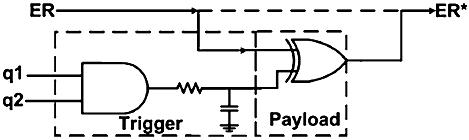

HT gồm hai khối [4, 5]: khối kích hoạt (trigger) và khối tải tin (payload).

Hình 3: Cấu tạo của HT [4]

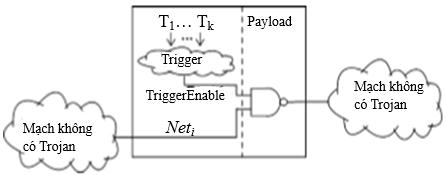

Khối kích hoạt thường là một mạch điện tử số tuần tự hoặc một mạch kết hợp để kiểm soát hoạt động tải tin và duy trì hoạt động ẩn các tác động của HT cho đến khi xảy ra điều kiện kích hoạt. Tải tin có thể ở dạng số hoặc tương tự được “cấy” chủ đích vào IC để gửi các tín hiệu gây hại theo điều kiện kích thích. Hình 4 thể hiện cơ chế hoạt động của HT ở mức cổng: các đầu vào (T1, T2, …, Tk) cấp cho khối kích hoạt lấy từ các đường dẫn (các net) khác nhau trong mạch. Còn khối tải tin nhận tín hiệu Neti (của mạch không có trojan) và tín hiệu đầu ra của khối kích hoạt (TriggerEnable). Do đó, khối kích hoạt sẽ nằm trong điều kiện hiếm (rare condition), đầu ra của khối tải tin hầu như luôn có cùng giá trị với Neti tại hầu hết các thời điểm. Tuy nhiên, khi khối Trigger bị kích hoạt, ví dụ TriggerEnable là “0”, thì đầu ra khối Payload sẽ khác biệt so với Neti. Điều này dẫn tới xung đột giữa các khối (tạo giá trị lỗi) trong mạch tổng hợp và gây ra lỗi ở đầu ra.

Hình 4: Cơ chế hoạt động của HT [4]

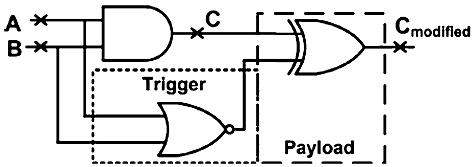

Các HT xuất hiện rất đa dạng, Hình 5 mô tả một mạch điện có Trojan kết hợp cùng với cổng NOR làm bộ kích hoạt và cổng XOR làm tải tin.

Hình 5: Mạch Trojan kết hợp [4]

Trojan này được kích hoạt khi điều kiện chỉ định: A=0 và B=0 xảy ra tại các nút kích thích ở cổng NOR, dẫn đến tải tin sẽ gửi ra tín hiệu đảo

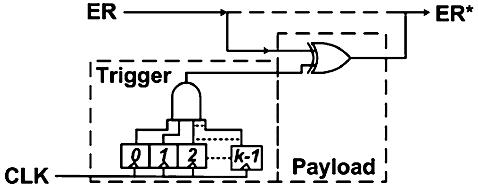

Hình 6 thể hiện một Trojan đồng bộ tuần tự (còn gọi là “bom hẹn giờ”) dùng một bộ đếm đơn để kích hoạt.

Hình 6: Mạch Trojan tuần tự [4]

Bộ kích hoạt chứa một bộ đếm k - bit và cổng AND, còn tải tin chứa một cổng XOR. Trojan này được kích hoạt sau khi xác lập 2k -1 nhịp đếm, để tạo ra một tín hiệu đảo ER*. Phiên bản dị bộ của Trojan này được thành lập bằng cách thay thế tín hiệu xung nhịp (CLK) bởi khối logic khác.

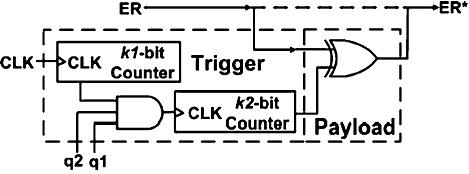

Hình 7 thể hiện một Trojan lai ghép, mạch này gồm cả bộ đếm đồng bộ (k1 - bit) và bộ đếm dị bộ (k2 - bit). Cả hai bộ đếm này cùng đạt các giá trị xác lập trước thì Trojan này mới kích hoạt để tạo ra tín hiệu đảo ER* của ER.

Hình 7: Mạch Trojan lai ghép [4]

Hình 8 thể hiện mạch Trojan tương tự, trong đó có một tụ điện nạp điện tích theo định kỳ khi đầu ra cổng AND (được điều khiển bởi q1 và q2) thiết lập ở mức 1, và tạo ra tín hiệu đảo ER*. Nếu đầu ra cổng AND không được thiết lập ở mức logic cao trong đúng khoảng thời gian định kỳ, thì tụ điện sẽ phóng điện tích xuống đất và Trojan sẽ không kích hoạt.

Hình 8: Mạch Trojan tương tự [4]

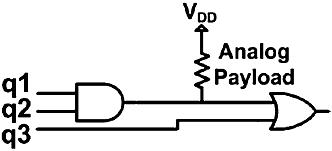

Các ví dụ trên đây đã chỉ ra rằng các HT kèm theo các bộ kích thích số hoặc kích thích tương tự sẽ đều đưa ra tải tin ở dạng số. Lưu ý rằng các tải tin số được thiết kế để tác động vào các giá trị logic số tại những nút chỉ định bên trong mạch. Hình 9 thể hiện tải tin tương tự khi xuất hiện lỗi, qua điện trở nối vào Vdd, lúc đó đầu ra của cổng AND sẽ có logic 0.

Hình 9: Trojan cấp tải tin tương tự qua Vdd [4]

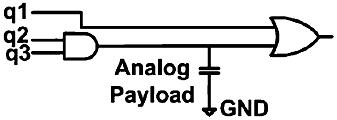

Còn Hình 10 thể hiện tải tin tương tự gây ảnh hưởng đến độ trễ đường dẫn tín hiệu, qua điện dung nối với GND, khi đó đầu ra của cổng AND sẽ có mức logic 1.

Hình 10: Trojan cấp tải tin qua GND [4]

Mối nguy hiểm đến từ HT

Trong thực tế, đã có nhiều nghiên cứu chứng minh mối nguy hiểm đền từ HT, như: HT được chèn vào quá trình chế tạo các IC bảo mật vô tuyến đã được công bố trong [7]. Các Trojan này được chèn vào lõi AES và khối phát băng tần siêu rộng (Ultra-wideband - UWB) của chipset ASIC (Application-Specific Integrated Circuit), gây rò rỉ khóa bí mật. Hoạt động của nó được ẩn giấu trong vùng dự trữ miền biên độ và tần số theo dung sai của tiến trình thiết kế chế tạo.

Một mối nguy hiểm khác về HT trong vi xử lý nhúng được trình bày trong công bố [8], được mô hình bởi máy trạng thái FSM tuần tự và bị kích hoạt bằng các lệnh điều khiển và xử lý dữ liệu theo trình tự chỉ định. Trojan này kích hoạt gây rò rỉ IP, khóa mã hóa và cũng làm sai chức năng của hệ thống.

Hay Trojan tin cậy là các biến thể độc hại sinh ra từ các điều kiện trong tiến trình chế tạo vật liệu bán dẫn, được giới thiệu trong công bố [9]. Các Trojan này khai thác các cơ chế hao mòn ở các lớp tiếp giáp của transistor CMOS, như tính không ổn định khi nhiệt độ bị định thiên âm (Negative Bias Temperature Instability - NBTI) hoặc chèn vào các hạt có hoạt tính cao (Hot Carrier Injection - HCI). Mục tiêu tấn công của Trojan này nhằm làm giảm độ tin cậy, hoạt hóa tuổi thọ linh kiện, gây lỗi cho IC nhớ (lỗi vùng nhớ cache_SRAM) và đặc biệt nguy hiểm khi tất cả các Trojan tin cậy này được kích hoạt tại cùng một thời điểm sử dụng.

Các Trojan nhỏ có hiệu năng tối ưu được thiết kế để tránh bị phát hiện trong các công bố [10]. Các Trojan này thường dựa vào các thay đổi khi điều chỉnh kích thước cổng logic, định tuyến lại các kết nối bên trong IC để chèn vào các cầu điện trở gây lỗi tại điểm nút xác định trong mạch điện. Chúng được thiết kế mà không gây ảnh hưởng về độ trễ đường dẫn tín hiệu, công suất tiêu thụ, diện tích vùng thiết kế của mạch tích hợp. Các mục tiêu tấn công của chúng nhằm leo thang đặc quyền, đáp ứng bất thường, xuất tín hiệu ra không phù hợp hoặc gây lỗi phần cứng.

Các mảng cổng khả trình (Field-programmable gate array - FPGA) và các hệ thống trên chip (SoC) cũng rất dễ bị tổn thương trước các tấn công của HT. Công bố [11] minh họa lược đồ phân tích tự động mức an toàn nhằm phát hiện ra các khai phá của Trojan trong SoC. Còn công bố [12] cũng đã trình bày cơ sở dữ liệu các tấn công Trojan có thể được dùng để chèn Trojan vào trong FPGA và SoC để nghiên cứu các kỹ thuật bảo vệ tin cậy và an toàn.

Kết luận

HT là nguy cơ hiện hữu đối với các IC bảo đảm an toàn phần cứng cho thiết bị nói riêng và thiết bị an ninh mạng nói chung. Các biến thể độc hại của chúng tiềm ẩn nhiều rủi ro đối với mọi thiết bị điện tử, hệ quả làm cho nền tảng phần cứng không còn được coi là “nguồn cội tin cậy”. Các HT được duy trì ở trạng thái tránh bị phát hiện và có thể không kích hoạt trong nhiều năm cho đến khi gặp điều kiện kích hoạt phù hợp. Để chống lại các tấn công của HT, yêu cầu cấp thiết là phải tiếp tục nghiên cứu về các mô hình hóa chính xác hoạt động của Trojan, các lược đồ phát hiện và xây dựng các biện pháp bảo vệ, ngăn chặn phù hợp.

|

TÀI LIỆU THAM KHẢO [1]. Semiconductor Industry Asociation (SIA), “Global billings report history (3-month moving average) 1976 - March 2009”, 2008. [2]. Wei Hu, Baolei Mao, Jason Oberg and Ryan Kastner, “Detecting Hardware Trojans with Gate – Level Information – Flow Tracking”, 2016. [3]. Leonel Acunha Guimaraes, “Testing Techniques for Detection of Hardware Trojans in Integrated Circuits of Trusted Systems”, 2018. [4]. Chakraborty, R.S., Narasimhan, S., and Bhunia, “S. Hardware Trojan: Threat and Emerging solutions”. In 2009 IEEE International High Level Design Validation and Test Workshop (Nov 2009), pp 166-171. [5]. Tehranipoor, M., and Wang, C. “Introduction to Hardware Security and Trust”. Springer Publishing Company, Incorporated, 2011. [6]. Jacob, N., Merli, D., Heyszl, J., and Sigl, G. “Hardware trojans: current challenges and approaches”. IET Computers Digital Techniques 8, 6 (2014). [7]. Y. Liu, Y. Jin, A. Nosratinia, Y. Makris, “Silicon demonstration of hardware Trojan design and detection in wireless cryptographic ICs”. IEEE Trans. Very Large Scale Integr. VLSI Syst. 25(4), 1506–1519 (2017). [8]. X. Wang, S. Narasimhan, A. Krishna, T. Mal-Sarkar, S. Bhunia, “Software exploitable hardware Trojan attacks in embedded processor”, in Proceedings of the IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT) (2012), pp. 55–58 [9]. Y. Shiyanovskii, F. Wolff, A. Rajendran, C. Papachristou, D. Weyer, W. Clay, “Process reliability based Trojans through NBTI and HCI effects”, in Proceeding of the NASA/ESA Conference on Adaptive Hardware and Systems (2010). [10]. B. Cha, S.K. Gupta, “A resizing method to minimize effects of hardware Trojans”, in 2014 IEEE 23rd Asian Test Symposium (2014), pp. 192–199 [11]. G.K. Contreras, A. Nahiyan, S. Bhunia, D. Forte, M. Tehranipoor, “Security vulnerability analysis of design-for-test exploits for asset protection in SoCs”, in 22nd Asia and South Pacific Design Automation Conference (2017), pp. 617–622 [12]. B. Shakya, T. He, H. Salmani, D. Forte, S. Bhunia, M. Tehranipoor, “Benchmarking of hardware Trojans and maliciously affected circuits”. J. Hardw. Syst. Secur. (HaSS) 1(1), 85–102 (2017) |

TS. Nguyễn Đức Công, ThS. Trần Thị Hạnh